1.音声データの伝送とデジタル信号処理

声帯や物質の振動で発生した音声は空気の振動としてマイクに届き、それが電気信号として音声処理装置に入力されます。そして何らかの処理が行われたものが電気信号として出力されて、スピーカーやイヤフォンによって音声が再生されます。これらの一連の流れは次の図のように表すことができます。

音声処理装置では次のような処理が行われます。

①増幅器

マイクロフォンからの微少なアナログ電気信号は、オペアンプ(増幅器の電子回路モジュール)によって増幅されてAD変換器に送られます。

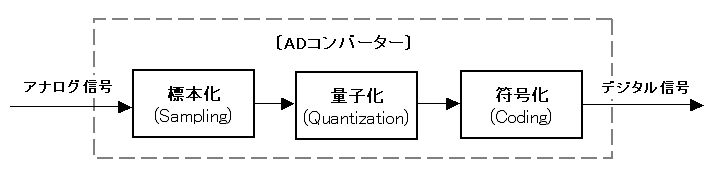

②AD変換器

アナログ信号をデジタル処理できるように、デジタル信号に変換します。ADC(アナログデジタル・コンバーター)とも呼ばれます。今回はこの部分を細かく見ていくことになります。

③MPU

MPUはMicro-processing unitの略で、音声信号をデジタル信号処理するプロセッサーです。今回のプロジェクトではRaspberry Pi Zeroがこれに相当します。デジタルフィルターなどにより音質や音量の調整を行います。

④DA変換器

MPUで処理されたデジタル信号を受けて、デジタル値をアナログの電圧値に変換します。DAC(デジタルアナログ・コンバーター)とも呼ばれます。

⑤増幅器

DA変換されたアナログ信号を音声として復元するために、スピーカーやイヤフォンなどを駆動するのに必要な電圧に増幅します。ここでもオペアンプが多用されます。

2.アナログ/デジタル変換の原理

アナログ/デジタル変換(A/D変換)は、図のように標本化、量子化、符号化の手順によってアナログ電気信号をデジタル電気信号に変換します。第8章でI2Sの音声データとPCM(Pulse Code Modulation:パルス符号変調)についてふれましたが、以下の変換プロセスによって音声信号からPCMデータが作成されます。

①標本化

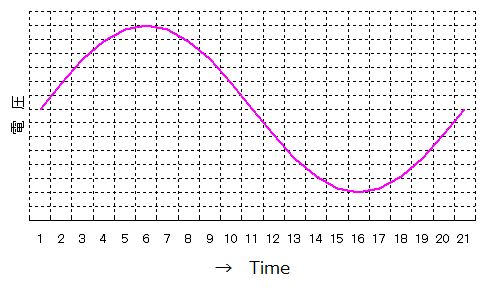

標本化はADコンバーターに入力されたアナログ信号を、一定時間で区切る操作です。下図・左は連続したアナログ信号です。時間経過をいくら細かく区切っても、その時々の電圧値を計測することができます。

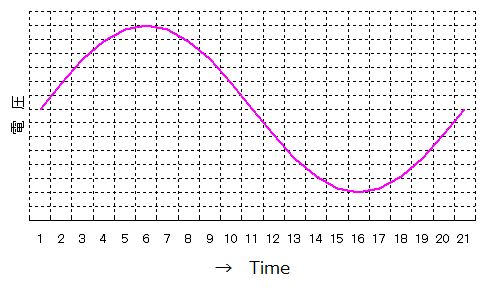

標本化では、時間とともに変化するアナログ信号を、その周波数より早い周波数(サンプリング周波数、サンプリングレートと呼びます)を使って分割し、一定間隔だけ保持(サンプルホールド)してそのタイミングごとの値を取り出します。下図・右にその状況を示します。こうすることで、連続したアナログ信号は時間軸で分割された「離散信号」に変わります。

このサンプリング周波数を高くすると、つまりサンプリングレートを大きくすると、変化をより細かく表現できることになります。これには「サンプリング定理」という重要な定理があって、入力信号の波形を正しく標本化するには、入力信号の最大周波数より2倍以上の周波数でおこなう必要があるとされています。この2倍の周波数は「ナイキスト周波数(またはナイキストレート)」と呼ばれます。

このサンプリング周波数を高くすると、つまりサンプリングレートを大きくすると、変化をより細かく表現できることになります。これには「サンプリング定理」という重要な定理があって、入力信号の波形を正しく標本化するには、入力信号の最大周波数より2倍以上の周波数でおこなう必要があるとされています。この2倍の周波数は「ナイキスト周波数(またはナイキストレート)」と呼ばれます。

ちなみに音楽CDのサンプリング周波数は44.1kHzですが、人間の聴感の最大周波数は20kHz程度ですから余裕をもって設定されていることがわかります。ナイキスト周波数より大幅に高いサンプリング周波数でサンプリングすることをオーバーサンプリングと言い、次で解説する量子化誤差を小さくすることができます。

②量子化

標本化されたデータをデジタル量に変換するのが量子化です。アナログ信号の最大電圧をフルスケールとして、これを何分割するかで分解能(Resolution)が決まります。分割数は二進数のビット数で決められ、これを量子化ビット数と呼びます。分解能が高いほど変化を精密に表現できます。先の音楽CDでは16ビットを採用しています。またCDより分解能が高いデジタルオーディオはハイレゾと呼ばれ、通常ではサンプリング周波数が96kHz以上で、24ビット以上の分解能をもっています。

| ・4ビット: | 2^4 | 16分割 |

| ・8ビット: | 2^8 | 256分割 |

| ・16ビット: | 2^16 | 65,536分割 |

| ・24ビット: | 2^24 | 1,677万分割 |

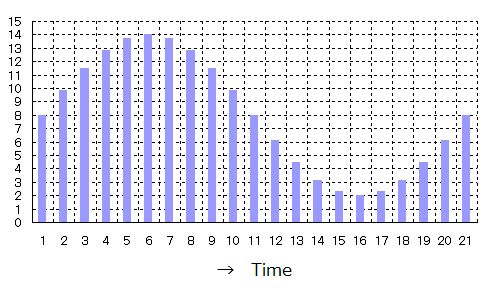

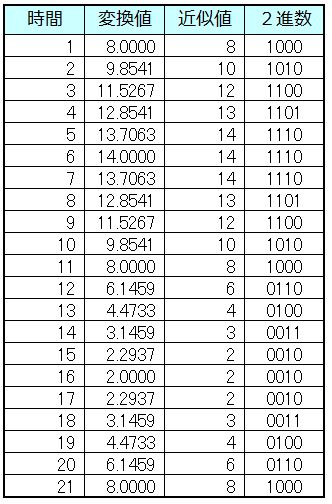

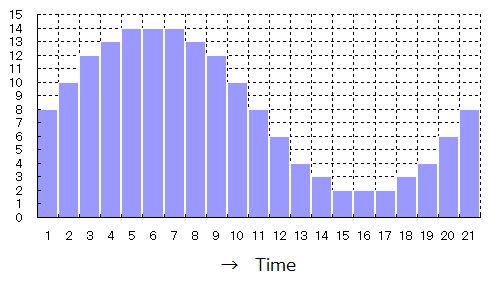

図のグラフは4ビットのケースで、値を16分割してそれぞれの時点の相対的な値を示しています。

変換された値は少数以下を含む実数値になりますが、デジタル化に先立って近似値の整数に変換します。表の「変換値」と「近似値」に見られるように、この変換(量子化)にともなって誤差が発生します。この量子化誤差は、本来の信号にないランダムノイズと高調波歪み、いわゆる量子化雑音を発生させる原因になります。

③符号化

近似値をグラフにすると右のようになります。

近似値をグラフにすると右のようになります。

この値を二進数に変換して(表の右列)出力するとデジタル信号(PCMデータ)の出来上がりです。実際には変換回路であるエンコーダーによって処理されます。

量子化雑音のほかに、アナログ信号とデジタル信号を相互変換するときに発生する別の現象があります。サンプリング周波数をfsとするとナイキスト周波数はfs/2ですが、このfs/2を超えた入力信号は帯域内に折り返されます。これは「折り返し(エリアシング:Aliasing)」と呼ばれる現象で、本来は存在しない成分が再生されて折り返し雑音の原因になります。

これを抑制するには十分に大きなサンプリング周波数とすること、あるいはアナログ信号の状態であらかじめナイキスト周波数より高い周波数成分をカットする電気回路のローパスフィルター(アンチエイリアシングフィルターとも)を設置することで対応します。

3.ADコンバーターの種類

ADコンバーターには次のような種類があります(出典:Wikipedia『アナログ-デジタル変換回路』)。

| 名 称 | サンプリングレート(Hz) | 分解能(bit) | 特 徴 | 用 途 |

| フラッシュ型 | 10G~10M | 12~6 | 高速・大規模 | 高速測定器 |

| パイプライン型 | 200M~10M | 14~8 | 映像・通信 | |

| 逐次比較型 | 1M~10k | 16~8 | 低消費電力 | マイコン |

| デルタシグマ型 | 10M~100 | 24~12 | 高分解能 | 音声処理、計測、通信 |

| 二重積分型 | 1k~10 | 22~12 | 高精度 | 計測 |

これからわかるように、音声処理やオーディオではデルタシグマ型(ΔΣ型)が主流です。

ΔΣ型ADCの特徴をもう少し細かくみると次の通りです。

・デジタルLSI技術の進歩が可能にした変換方式である。

・CMOS化に適した変換方式で、低消費電力、低コストである。

・高分解能(~24bit)で、すぐれた微分直線性をもっている。

・ダイナミックレンジを活かした音声帯域やオーディオ分野への応用に最適である。

初期のΔΣ型ADCはサンプリングレート数百Hzが限度で、分解能も16ビット以上は望めませんでした。その後の製造技術や回路技術の進歩によって200KHz、24ビット程度までが可能になり、コンパクトな半導体デバイスのパッケージとして提供されています。

そこで、以下ではデルタシグマ型に絞って動作の詳細を把握しておきましょう。

4.ΔΣ型ADコンバーターの動作原理

ΔΣ型ADCがどのようなものかについての概説は多いのですが、それがどのように動作しどのように変換処理を行うのかを説明している資料が見あたりません。個別製品のデータシートやユーザーガイドは、これらのことは既知のこととして専門的な内容が詳述されていて、理解するのは簡単ではありません。

そのような折りに、きわめて詳細かつ明快に解説しているサイトを見つけました。株式会社東陽テクニカの『AD変換の基礎/第5回デルタシグマAD変換器』がそれで、以下にその内容を引用・要約して解説します。

シグマデルタ型ADコンバーターは、従来のADコンバーターのように入力信号の絶対振幅を記録するのと異なり、信号振幅の変化を記録し、それを1bit量として保存します。

下図はシグマデルタ型ADコンバーターのブロック図です。以下では順を追ってコンバーターの動作とデータの変遷を説明します。図と末尾のデータ変遷表を参照してください。なお、説明はデータ変遷表のサイクルナンバー2から始まっています。

ⓐアナログ信号入力

信号を大幅にオーバーサンプリングすることにより、便宜上、入力はDC信号としてシンプルに考える事ができます。

今回は、リファレンス電圧Vrefの3/4倍(3/4Vref)が入力され続けた場合について考えます。

ⓑフィードバックとの差異(Difference amplifier)

変換器はフィードバック・ループを基本にして動作します。

ここでは、1 Vrefのネガティブフィードバックがあったとして考えます。

その結果、ⓑでの値は「3/4 Vref - 1 Vref = -1/4Vref」になります。

ⓒ積分器(Integrator)

積分器の過去の出力を新しい入力値に加える役割を果たします。

従って、ⓑでの値に依存して、積分器からの出力は増加、もしくは減少します。

今回の例では、積分器からの出力は「-1/4 Vref + 3/4 Vref = 2/4 Vref」となります。

ⓓ比較器(Comparator)

このコンポーネントは入力された値を0Vのリファレンスと比較します。比較器からの出力はデジタル信号です。

比較器への入力値がリファレンス値になる時、出力値は1から0、もしくは反対に0から1に反転します。

今回の例では、入力値2/4 Vrefがリファレンス値よりも大きいため、出力値は1です。

ⓔフィードバック

比較器からの出力は1bit-DAコンバーターに入ります。

このコンポーネントでは、単に、入力値が1の時は1Vrefを、入力値が0の時は-1 Vrefを出力します。

このサイクルでは、比較器からのデジタル信号はDA変換器を通して、ⓐへのフィードバックは1Vrefになります。

以下をすべてのサイクルで繰り返すと、ⓓには次々に変換された二進数が現れます。

比較器から出力されるデジタル信号は、シグマデルタ型ADコンバーターの出力そのものになります。このことから、コンバーターはパルス幅変調器であると言うこともできます。このⓓを眺めると、今回の例ではデジタル信号0に対する1の割合は7/8になっています。

今、-1 Vref ~1 Vrefの範囲を1/4 Vref ステップ幅で分割すると、8 + 1 = 9つのステップ(入力値として処理可能な値)を作ることができます。最も小さな値(-1 Vref)を0/8、最も大きな値(1 Vref)を8/8に対応させると、7/8は3/4 Vrefに相当し、まさに入力したDC信号を表しています。

直感的にいえば、シグマデルタ型AD変換器では、基本的に、現在の値を過去の値と比較し、現在の値が昔の値よりも高ければΔV、低ければ-ΔVを加えていると言えます。

〔ΔΣ型ADコンバーターモデルのデータ変遷表〕

(ここでⓐ~ⓒの数値はリファレンス電圧 Vrefの比率)

| サイクル | アナログⓐ | 差異ⓑ | 積分ⓒ | 0との比較ⓓ | フィードバックⓔ |

| 0 | 3/4 | 0 | 0 | 0 | 0 |

| 1 | 3/4 | 3/4 | 3/4 | 1 | 1 |

| 2 | 3/4 | -1/4 | 2/4 | 1 | 1 |

| 3 | 3/4 | -1/4 | 1/4 | 1 | 1 |

| 4 | 3/4 | -1/4 | 0 | 0 | -1 |

| 5 | 3/4 | 7/4 | 7/4 | 1 | 1 |

| 6 | 3/4 | -1/4 | 6/4 | 1 | 1 |

| 7 | 3/4 | -1/4 | 5/4 | 1 | 1 |

| 8 | 3/4 | -1/4 | 4/4 | 1 | 1 |

| 9 | 3/4 | -1/4 | 3/4 | 1 | 1 |

| 10 | 3/4 | -1/4 | 2/4 | 1 | 1 |

| 11 | 3/4 | -1/4 | 1/4 | 1 | 1 |

| 12 | 3/4 | -1/4 | 0 | 0 | -1 |

| 13 | 3/4 | 7/4 | 7/4 | 1 | 1 |

| 14 | 3/4 | -1/4 | 6/4 | 1 | 1 |

| 15 | 3/4 | -1/4 | 5/4 | 1 | 1 |

| 16 | 3/4 | -1/4 | 4/4 | 1 | 1 |

| 17 | 3/4 | -1/4 | 3/4 | 1 | 1 |

| 18 | 3/4 | -1/4 | 2/4 | 1 | 1 |

以上からわかるように、シグマデルタ型AD変換器の精度はDA変換器内のリファレンス電圧の精度に大きく影響されます。この値にわずかな誤差があると、まったく違った値が出力されてしまいます。シグマデルタ方式では、Vrefは信号に毎サイクル加えられているため、その精度は生命線とも言えます。

アナログ/デジタル変換の仕組みがわかり、今後のADコンバーターとしてはΔΣ型を選択すればよいことや、使用上の注意点などを知ることができました。次回は、今後の音声信号を観測したり解析するための小道具となるソフトを導入します。お楽しみに!